Tại sao các nhà sản xuất chip không tăng kích thước chip để tăng số lượng transistor mà phải tìm mọi cách để thu hẹp chip?

Không chỉ vì các nguyên nhân từ hiệu năng và hiệu quả năng lượng, nỗ lực thu hẹp kích thước chip còn đem lại các lợi thế vượt trội về tính kinh tế, cho dù đánh đổi lại là những khoản đầu tư khổng lồ về công nghệ sản xuất.

*Lược dịch câu trả lời của Luc Boulesteix với sự đồng thuận của Sebastian Dadeby, thạc sĩ khoa học ngành Thiết kế hệ thống và Kỹ sư điện, Đại học công nghệ Chalmers.

Rõ ràng việc thu hẹp tiến trình sản xuất chip để gia tăng số lượng và mật độ bóng bán dẫn là việc ngày càng khó khăn và tốn kém, vậy tại sao các công ty sản xuất chip không xây dựng các die chip (hay các đế chip) để gia tăng số lượng bóng bán dẫn, thay vì phải vất vả tìm cách thu hẹp tiến trình và kích thước die chip?

Tuy nhiên, câu hỏi chính xác nhất cho điều này nên là, tăng kích thước die chip để làm gì?

Các nhà sản xuất hoàn toàn có thể làm các chip với kích thước lớn hơn, nhưng có lẽ nó sẽ chẳng mang lại nhiều ý nghĩa. Nguyên nhân đơn giản của việc này là vì người ta cần đặt con chip vào vừa trong thiết bị, một con chip mạnh mẽ sẽ trở nên vô nghĩa nếu nó không thể đặt vừa trong thiết bị cần dùng.

Dưới đây là hình ảnh của chip GV100, GPU do Nvidia thiết kế. Nó có đầy sức mạnh và có diện tích lên tới 852mm2. Liệu bạn có thể đặt nó vào trong chiếc smartwatch không?

GPU Quadro GV100 của Nvidia.

Tuy nhiên, chắc chắn những con chip kích thước lớn như thế này sẽ có chỗ trong các máy tính desktop hoặc máy chủ, vốn ít quan tâm đến các giới hạn về kích thước. Nếu nhìn vào các con chip dành cho máy chủ hoặc siêu chip HEDT (High-End Desktop), bạn sẽ thấy các die chip này càng ngày càng rộng hơn, lớn hơn để chứa nhiều nhân xử lý hơn.

Ngay cả như vậy, vẫn có một giới hạn thực tế cho kích thước tối đa của các con chip này, không chỉ vì để có thể đặt vừa trong thiết bị của mình mà đó còn là kích thước thực tế chúng ta có thể sản xuất.

Các giới hạn trong sản xuất chip

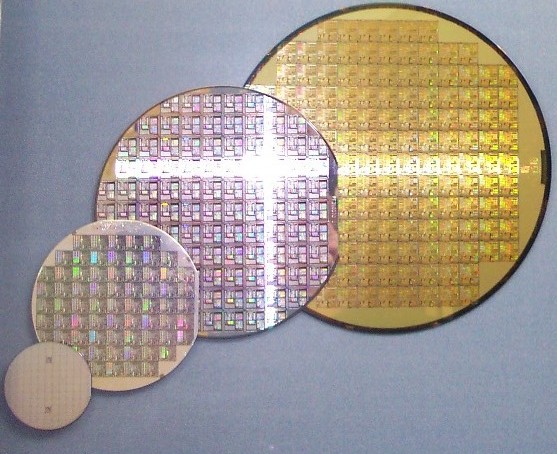

Đầu tiên, các micro chip đều được cắt ra từ các tấm bán dẫn lớn hơn được gọi là các đĩa wafer. Đó là các đĩa silicon hình tròn có đường kính 300mm như bạn thường thấy ngày nay. Và rõ ràng đó không phải là những chiếc đĩa có kích thước vô hạn.

Điều này có nghĩa là các nhà sản xuất có thể thu được nhiều chip hơn trên một đĩa wafer này nếu kích thước của mỗi con chip giảm xuống. Ngược lại, số lượng chip trên mỗi đĩa wafer sẽ giảm đi nếu kích thước của chúng tăng lên. Và điều này cũng đúng nếu ta tăng kích thước die chip lên, die chip lớn hơn tương đương với số lượng chip trên mỗi đĩa wafer ít hơn, và ngược lại.

Video đang HOT

Các loại đĩa wafer với các kích thước khác nhau.

Ngành sản xuất bán dẫn là một ngành có độ chính xác khắt khe đến mức đáng kinh ngạc, nhưng nó vẫn không hoàn hảo. Không phải toàn bộ các die chip được khắc trên đĩa wafer đều có thể sử dụng được, khi một số khuyết tật có thể xuất hiện ngẫu nhiên trên các đĩa đó (ví dụ một vài hạt bụi hoặc vết bẩn nào đó).

Bất kỳ con chip nào được xây dựng trên tại vị trí bị khuyết tật đó đều được xem như hỏng hoàn toàn và không thể sửa chữa được. Điều này luôn có thể xảy ra cho dù con chip đó có kích thước lớn hay nhỏ. Và đây là một vấn đề trong việc xác định chi phí sản xuất cho mỗi con chip.

Trong khi chi phí cho nguyên vật liệu cho mỗi con chip tương đồng với kích thước die chip – die chip càng lớn thì kích thước càng tăng – nhưng số lượng thực sự các chip có thể hoạt động trên một đĩa wafer lại không hoàn toàn như vậy.

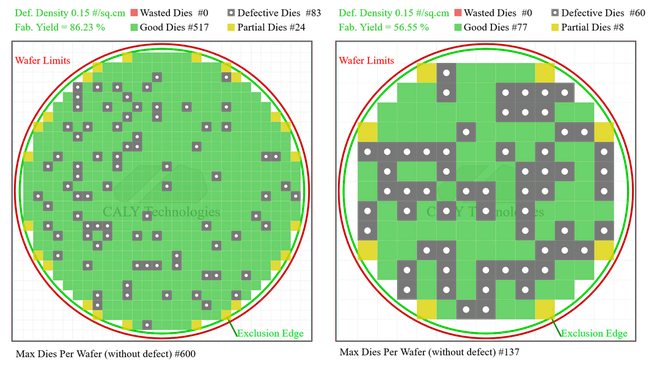

Chi phí cho mỗi đĩa wafer là cố định, vì vậy số lượng chip có thể hoạt động ít hơn nghĩa là chi phí trên mỗi chip cũng cao hơn, kéo theo chi phí sản xuất cho mỗi chip này cũng tăng lên theo. Thử so sánh năng suất sản xuất giữa các die chip diện tích 100mm2 và 400mm2 trên một đĩa wafer 300mm (giả sử cả hai đều có mật độ khuyết tật là 0,15 khuyết tật trên mỗi cm2) như hình vẽ dưới đây.

So sánh số lượng chip nguyên vẹn thu được trên mỗi đĩa wafer

Bạn sẽ thấy tỷ lệ các chip hoạt động với các chip chết giữa hai loại die chip không giống nhau. Dù cùng một tỷ lệ khuyết tật, nhưng số lượng chip chết trên die chip 400mm2 nhiều hơn so với die chip 100mm2.

Nếu chúng ta giả sử mỗi đĩa wafer sẽ có giá khoảng 10.000 USD, vì vậy chúng ta sẽ có chi phí cho mỗi chip vào khoảng 19,34 USD cho mỗi chip die 100mm2 và vào khoảng 129,87 USD cho mỗi chip die 400mm2. Nghĩa là khi bạn tăng kích thước die chip lên 4 lần, chi phí cho mỗi chip tăng lên gấp hơn 6,71 lần. Chênh lệch này còn lớn hơn nữa khi bạn tăng diện tích chip lên: ví dụ với diện tích die chip là 625mm2, chi phí cho mỗi chip sẽ vào khoảng 294,1 USD, nghĩa là chi phí cao gấp hơn 15,2 lần cho việc tăng diện tích lên thêm 6,25 lần.

Đây chính là giới hạn thực tế của việc sản xuất các chip có kích thước lớn: chi phí sẽ gia tăng theo cấp số nhân so với việc tăng diện tích die chip. Không có cách nào có thể tạo ra các con chip lớn hơn trong khi vẫn giữ được tính kinh tế.

Năng lượng và các hạn chế về thiết kế

Tăng cường thêm mật độ bóng bán dẫn không phải là nguyên nhân duy nhất cho việc các nhà sản xuất liên tục tìm cách chuyển sang các tiến trình nhỏ hơn: bên cạnh nhiều ưu điểm khác, các bóng bán dẫn nhỏ hơn sẽ sử dụng ít năng lượng hơn.

Trong khi một con chip lớn hơn dù có nhiều bóng bán dẫn hơn, nhưng lại không làm các bóng bán dẫn đó có hiệu quả năng lượng cao hơn. Bạn vẫn có thể tích hợp thêm một số tính năng lên die chip kích thước lớn đó, nhưng mức tiêu thụ năng lượng trên mỗi bóng bán dẫn vẫn sẽ giữ nguyên, với cùng tần số và điện thế.

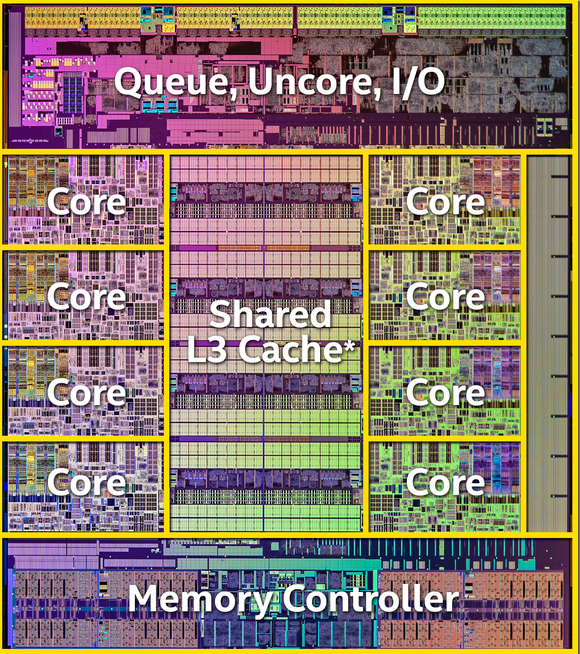

Die chip của Intel Core i7-5960X với 8 lõi 16 luồng ra mắt năm 2014.

Điều đó sẽ kéo theo một giới hạn khác: đó là về điện năng tiêu thụ của mỗi thiết bị. Đối với các máy tính desktop, điện năng tiêu thụ cao sẽ cần có thêm các bộ phận tản nhiệt và làm mát. Còn đối với các thiết bị di động, giới hạn về điện năng sẽ càng trở nên quan trọng hơn khi chúng đều chạy bằng pin.

Để đảm bảo thời lượng pin đối với các con chip lớn hơn, bạn sẽ cần giảm điện thế hoạt động và xung nhịp của nó xuống. Tất nhiên điều này cũng làm mất đi một số lợi thế về hiệu năng gia tăng dựa trên việc gia tăng số lượng bóng bán dẫn.

Hơn nữa đối với các nhà thiết kế chip, việc gia tăng kích thước thực sự là một cơn ác mộng: các tín hiệu điện chỉ có một tốc độ giới hạn khi di chuyển từ dây nối sang vật liệu bán dẫn. Nếu bạn gia tăng kích thước chip, cũng có nghĩa sẽ làm gia tăng khoảng cách một tín hiệu cần phải di chuyển để tới được các bộ phận chức năng khác.

Với hàng kilomet dây dẫn bên trong mỗi con chip hiện đại, khi tăng khoảng cách di chuyển của tín hiệu, mọi thứ sẽ trở nên phức tạp rất nhanh. Sử dụng tất cả các bóng bán dẫn một cách hiệu quả sẽ trở thành một thách thức đáng kể khi ta nới rộng các khoảng cách đó lên.

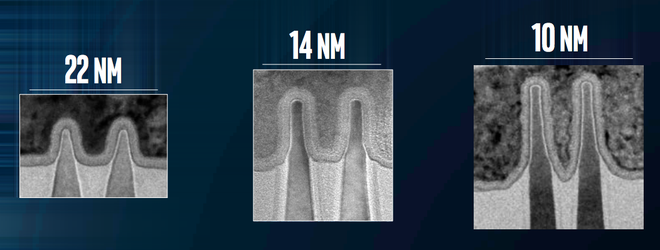

Bắt đầu từ tiến trình 22nm, thay vì thu hẹp kênh dẫn giữa các cực trên bóng bán dẫn, các nhà sản xuất chuyển chọn cách nâng cao các cực source và drain trên chip và thu hẹp khoảng cách giữa chúng, nhằm giảm kích thước bóng bán dẫn và gia tăng mật độ của chúng trên chip.

Thêm vào đó, việc gia tăng kích thước chip còn kéo theo nhiều vấn đề khác: làm sao bạn có thể đồng bộ một xung tín hiệu (một clock signal) khi nó không thể truyền qua con chip trong một chu kỳ xung nhịp đó. Làm thế nào bạn có thể truyền một rãnh năng lượng thông qua đó? Nếu bạn không chú ý đến vấn đề này, một số khu vực trong con chip có thể bị mất điện cục bộ nếu tải công việc thay đổi đột ngột.

Khi không thể xây dựng các con chip lớn hơn để tăng cường hiệu năng, các nhà sản xuất không còn cách nào khác ngoài việc chạy đua thu hẹp tiến trình chip. Khi số lượng bóng bán dẫn và khoảng cách giữa chúng trên chip phẳng đã không thể gia tăng được nữa, các nhà sản xuất đã chuyển sang phương pháp tích hợp hàng dọc với các thiết kế 2,5D và 3D FinFET.

Dù chúng không thể giải quyết toàn bộ các vấn đề liên quan đến phương pháp tích hợp hàng ngang, nhưng nó vẫn mang tới một số ưu điểm quan trọng, bao gồm thu hẹp kích thước die chip và giảm đáng kể chi phí.

Theo GenK

Sau Qualcomm, những nhà sản xuất khác cũng bước vào cuộc đua 5G

Bên cạnh việc thống trị thị trường chip xử lý di động, Qualcomm cũng là nhà sản xuất đầu tiên cung cấp các modem 5G.

Mặc dù đang dẫn đầu, nhưng tiếp sau Qualcomm, các nhà sản xuất khác cũng bắt đầu tham gia vào cuộc đua 5G với các modem riêng như Samsung, Huawei,... sẽ được ra mắt trong năm 2020.

Modem 5G của Samsung và Huawei

Sau Qualcomm, Samsung và Huawei cũng đã công bố modem đa chế độ 4G/5G với tên gọi là Exynos 5100 và Balong 5000. Cả hai công ty đều có các sản phẩm cung cấp mạng 2G, 3G, 4G và 5G trong một modem. Điều quan trọng là các modem này sẽ xuất hiện bên trong SoC vào năm 2020, cung cấp các giải pháp tiết kiệm năng lượng cho các điện thoại 5G.

Exynos 5100 được sản xuất theo quy trình 10nm với tốc độ dữ liệu tối đa là 2 GB/s khi sử dụng phổ tần Sub-6Ghz và 6 GB/s khi sử dụng phổ tần mmWave.

Huawei Balong 5000 cũng có tốc độ cực nhanh, ở mức phổ Sub-6GHz chip có thể tải xuống với tốc độ 4.6 GB/s và tốc độ tải lên 2.5 GB/s. Còn khi sử dụng phổ mmWave, tốc độ tải xuống đạt tối đa 6.5 GB/s và 3.5 GB/s tốc độ tải lên (khi kết hợp với luồng dữ liệu LTE, tốc độ tải xuống có thể đạt tới 7.5 GB/s). Balong 5000 hỗ trợ cả mạng 5G độc lập và không độc lập.

Các nhà sản xuất chờ đợi tới thời điểm 5G là xu hướng chính

Việc trở thành nhà sản xuất đầu tiên hỗ trợ 5G sẽ là một chiến thắng lớn về mặt thương hiệu, tuy nhiên không cần phải quá vội tìm cách chiến thắng. Vì sẽ có rất ít người dùng có thể truy cập thường xuyên vào mạng 5G trong năm 2019, chưa kể các điện thoại 5G đầu tiên sẽ gặp một số vấn đề về hiệu năng và thời lượng sử dụng.

Ra mắt đúng sản phẩm vào đúng thời điểm người dùng thực sự bắt đầu sử dụng 5G có thể sẽ là công thức chiến thắng. Theo Tổng giám đốc chiến lược 5G của Intel - Rob Topol cho biết, công ty đang chờ đợi thời điểm 5G trở thành xu hướng chính. Công ty cũng có kế hoạch để ra mắt modem 5G vào năm 2020 (có thể là iPhone 2020) khi người dùng sử dụng dịch vụ 5G nhiều hơn.

Intel sẽ gia nhập thị trường với chip đa chế độ từ 2G tới 5G, hỗ trợ cho mạng 5G độc lập - Modem XMM 8160 5G sẽ có tốc độ tải xuống là 6 GB/s và tương thích với nhiều điện thoại, máy tính bảng, PC, IoT, xe hơi,... Intel cũng thực hiện rất nhiều công việc để phát triển máy chủ 5G.

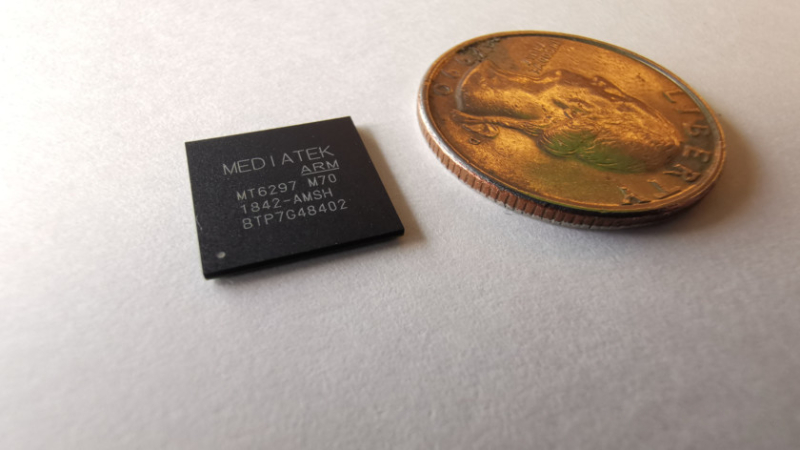

Một tên tuổi lớn khác đã âm thầm thực hiện kế hoạch 5G là MediaTek. Bên cạnh modem M70 5G công bố vào cuối năm ngoái có tốc độ tải xuống 4.7 GB/s và tốc độ tải lên 2.5 GB/s, công ty cũng đang phát triển một chip xử lý theo quy trình 7nm để xuất hiện trên các điện thoại ra mắt vào năm 2020. MediaTek vẫn chưa xác nhận việc liệu SoC hàng đầu thế hệ kế tiếp này có được tích hợp modem 5G hay không.

Một thương hiệu khác có trụ ở tại Trung Quốc cũng đang tham gia chạy đua 5G là UniSOC, công ty phát triển một số SoC smartphone với chi phí hiệu quả. Vì thế hãng có thể trở thành một ông lớn trong thị trường 5G nhờ các sản phẩm hỗ trợ 5G có giá thành rẻ - sử dụng modem UniSOC UDX710 5G. Con chip này hỗ trợ đa chế độ từ 2G tới 5G và được thiết kế theo quy trình 12nm.

Lời kết

Những thiết bị đầu tiên trang bị Snapdragon X50 sẽ không hỗ trợ đa chế độ, tiêu thụ điện năng nhiều hơn bởi modem 5G được thêm vào và không hỗ trợ tiêu chuẩn 5G độc lập. Tuy nhiên các modem ra mắt vào năm 2020 sẽ hỗ trợ LTE và 5G chỉ trong một con chip, đồng thời hỗ trợ cả 5G độc lập.

Nguồn: AndroidAuthority

Apple gặp khó khăn khi không thể chọn ai làm nhà cung cấp modem 5G cho iPhone  iPhone 2019 dự kiến sẽ có một phiên bản 5G, tuy nhiên cho đến nay, Apple vẫn chưa thể lựa chọn ai là nhà cung cấp modem 5G cho mình. Qualcomm và Samsung là những nhà sản xuất modem 5G có thể đáp ứng được các tiêu chuẩn cao của Apple. Apple đang rạn nứt với Qualcomm, vì vậy mà Apple đang rơi...

iPhone 2019 dự kiến sẽ có một phiên bản 5G, tuy nhiên cho đến nay, Apple vẫn chưa thể lựa chọn ai là nhà cung cấp modem 5G cho mình. Qualcomm và Samsung là những nhà sản xuất modem 5G có thể đáp ứng được các tiêu chuẩn cao của Apple. Apple đang rạn nứt với Qualcomm, vì vậy mà Apple đang rơi...

Thực hư tin Campuchia điều binh sĩ tới biên giới với Thái Lan sau vụ đối đầu08:43

Thực hư tin Campuchia điều binh sĩ tới biên giới với Thái Lan sau vụ đối đầu08:43 Video sốc: Chụp ảnh check in, thanh niên 20 tuổi bất ngờ bị sóng "nuốt gọn" ngay trước mắt bạn bè00:31

Video sốc: Chụp ảnh check in, thanh niên 20 tuổi bất ngờ bị sóng "nuốt gọn" ngay trước mắt bạn bè00:31 Ngô Thanh Vân lộ video vòng 2 lùm lùm trong tiệc sinh nhật, có động thái che chắn nhưng không đáng kể!01:15

Ngô Thanh Vân lộ video vòng 2 lùm lùm trong tiệc sinh nhật, có động thái che chắn nhưng không đáng kể!01:15 Đôi Vbiz "phim giả tình thật" đang sống chung nhà, bí mật bại lộ bởi 1 tíc tắc diễn ra trên sóng livestream00:46

Đôi Vbiz "phim giả tình thật" đang sống chung nhà, bí mật bại lộ bởi 1 tíc tắc diễn ra trên sóng livestream00:46 Xót xa tiếng khóc bất lực của nữ chủ quán Đà Nẵng khi chứng kiến toàn bộ phòng trà bị thiêu rụi ngay trước mắt00:25

Xót xa tiếng khóc bất lực của nữ chủ quán Đà Nẵng khi chứng kiến toàn bộ phòng trà bị thiêu rụi ngay trước mắt00:25 Vì sao Văn Toàn dễ dàng cho Hoà Minzy vay 4 tỷ nhưng lần thứ hai cô bạn thân hỏi vay tiếp thì say "No"?00:44

Vì sao Văn Toàn dễ dàng cho Hoà Minzy vay 4 tỷ nhưng lần thứ hai cô bạn thân hỏi vay tiếp thì say "No"?00:44 Xung đột Nga - Ukraine trước bước ngoặt08:59

Xung đột Nga - Ukraine trước bước ngoặt08:59 Khoảnh khắc "tiên tử kết màn" gây bão của người đàn ông tóc xanh mặc đẹp số 1 Hàn Quốc05:14

Khoảnh khắc "tiên tử kết màn" gây bão của người đàn ông tóc xanh mặc đẹp số 1 Hàn Quốc05:14 Tiếng khóc nghẹn của nữ sinh tố cáo chủ trọ hành hung vì tiền đặt cọc ở Hà Nội00:27

Tiếng khóc nghẹn của nữ sinh tố cáo chủ trọ hành hung vì tiền đặt cọc ở Hà Nội00:27 Video: Va chạm giao thông, 2 người phụ nữ xô xát với người đàn ông lớn tuổi00:20

Video: Va chạm giao thông, 2 người phụ nữ xô xát với người đàn ông lớn tuổi00:20 Ca sĩ Mỹ Tâm ăn tối sang chảnh ở Mỹ, Lý Nhã Kỳ gợi cảm00:52

Ca sĩ Mỹ Tâm ăn tối sang chảnh ở Mỹ, Lý Nhã Kỳ gợi cảm00:52Tin đang nóng

Tin mới nhất

Nâng cao và biến đổi hình ảnh của bạn bằng trình chỉnh sửa video trực tuyến CapCut

Cách đăng Facebook để có nhiều lượt thích và chia sẻ

Thêm nhiều bang của Mỹ cấm TikTok

Microsoft cấm khai thác tiền điện tử trên các dịch vụ đám mây để bảo vệ khách hàng

Facebook trấn áp hàng loạt công ty phần mềm gián điệp

Meta đối mặt cáo buộc vi phạm các quy tắc chống độc quyền với mức phạt 11,8 tỷ đô

Không cần thăm dò, Musk nên sớm từ chức CEO Twitter

Đại lý Việt nhập iPhone 14 kiểu 'bia kèm lạc'

Khai trương hệ thống vé điện tử và dịch vụ trải nghiệm thực tế ảo XR tại Quần thể Di tích Cố đô Huế

'Dở khóc dở cười' với tính năng trợ giúp người bị tai nạn ôtô của Apple

Xiaomi sa thải hàng nghìn nhân sự

Apple sẽ bắt đầu sản xuất MacBook tại Việt Nam vào giữa năm 2023

Có thể bạn quan tâm

Phượng Singapore mỗi bữa nấu gần 30 món, chao đảo MXH vì 'tốc độ' là ai?

Netizen

17:59:25 01/03/2025

Sao Hoa ngữ 1/3: Trương Quân Ninh tiết lộ cảnh tình tứ với Liên Bỉnh Phát

Sao châu á

17:49:49 01/03/2025

Hương Tươi: 'Tôi không còn hụt hẫng khi quá tuổi đóng vai chính'

Sao việt

17:46:40 01/03/2025

Tử vi 12 con giáp thứ Bảy ngày 1/3/2025: Thân quá khắt khe, Dậu gặp trở ngại

Trắc nghiệm

17:40:27 01/03/2025

Văn Toàn đóng MV của Hòa Minzy, dân mạng nhiệt tình "đẩy thuyền"

Nhạc việt

17:30:28 01/03/2025

Israel đề xuất gia hạn giai đoạn 1 của thỏa thuận ngừng bắn tại Gaza

Thế giới

17:23:50 01/03/2025

Côn đồ ngông cuồng mang kiếm 'gặp đâu chém đó'

Pháp luật

16:45:39 01/03/2025

Cuối tuần tranh thủ làm món bánh "chiêu tài" này ăn, vừa ngon lại tốt cho sức khỏe

Ẩm thực

16:42:24 01/03/2025

Loài thực vật săn mồi có lá giống hệt rắn hổ mang

Lạ vui

16:24:08 01/03/2025

Vợ đẹp của Lâm Tây gây tranh cãi khi tập gym chỉ sau 10 ngày sinh con, lên tiếng cảnh báo: Đừng như Xuân!

Sao thể thao

16:22:18 01/03/2025

Mini-hack: Apple đã dạy tôi một cuộc sống không cần có ứng dụng quản lý file (như Windows Explorer)

Mini-hack: Apple đã dạy tôi một cuộc sống không cần có ứng dụng quản lý file (như Windows Explorer) Apple, Google và Netflix giờ đây không còn yêu cầu nhân viên phải có bằng Đại học

Apple, Google và Netflix giờ đây không còn yêu cầu nhân viên phải có bằng Đại học

Huawei tham vọng vượt Samsung để trở thành nhà sản xuất smartphone số 1 thế giới

Huawei tham vọng vượt Samsung để trở thành nhà sản xuất smartphone số 1 thế giới Huawei có thể trở thành nhà sản xuất smartphone dẫn đầu thị trường

Huawei có thể trở thành nhà sản xuất smartphone dẫn đầu thị trường Phụ thuộc quá nhiều vào đối tác Trung Quốc, Apple có thể đang tự hại chính mình

Phụ thuộc quá nhiều vào đối tác Trung Quốc, Apple có thể đang tự hại chính mình Huawei tăng trưởng lợi nhuận kỷ lục, doanh thu lần đầu tiên vượt mốc 100 tỷ USD

Huawei tăng trưởng lợi nhuận kỷ lục, doanh thu lần đầu tiên vượt mốc 100 tỷ USD Nhà sản xuất ống kính Largean Precision chật vật vì doanh số iPhone sụt giảm

Nhà sản xuất ống kính Largean Precision chật vật vì doanh số iPhone sụt giảm BOE đang cạnh tranh với Samsung để kiếm được hợp đồng từ Apple

BOE đang cạnh tranh với Samsung để kiếm được hợp đồng từ Apple Ninh Thuận: Người phụ nữ lượm ve chai bị sát hại

Ninh Thuận: Người phụ nữ lượm ve chai bị sát hại HOT: Á hậu Miss Universe Vietnam được cầu hôn, nhẫn kim cương "to vật vã" chứng minh vị hôn phu "không phải dạng vừa"!

HOT: Á hậu Miss Universe Vietnam được cầu hôn, nhẫn kim cương "to vật vã" chứng minh vị hôn phu "không phải dạng vừa"! Nam nghệ sĩ bức xúc chỉ tay, nói thẳng mặt những người thiếu tôn trọng mình trong họp báo

Nam nghệ sĩ bức xúc chỉ tay, nói thẳng mặt những người thiếu tôn trọng mình trong họp báo Sốc: Á quân Rap Việt bị tung bài diss tố "tác động vật lý" phụ nữ, bức ảnh được tung ra gây kinh hãi

Sốc: Á quân Rap Việt bị tung bài diss tố "tác động vật lý" phụ nữ, bức ảnh được tung ra gây kinh hãi

"Bóc" độ xa hoa và quy định trong đám cưới "cơ trưởng đẹp trai nhất Việt Nam" và phú bà U30 diễn ra hôm nay!

"Bóc" độ xa hoa và quy định trong đám cưới "cơ trưởng đẹp trai nhất Việt Nam" và phú bà U30 diễn ra hôm nay! "Nam thần mơ ước của các cô gái" lộ nhan sắc thật qua cam thường

"Nam thần mơ ước của các cô gái" lộ nhan sắc thật qua cam thường Nữ nghệ sĩ đình đám đã bán nốt biệt thự 70 tỷ ở Việt Nam

Nữ nghệ sĩ đình đám đã bán nốt biệt thự 70 tỷ ở Việt Nam Người mẹ nguy kịch vì bị con trai tạt xăng dã man: "Tôi không bao giờ giận con..."

Người mẹ nguy kịch vì bị con trai tạt xăng dã man: "Tôi không bao giờ giận con..." Thêm 1 sao Việt tung tin nhắn, "bóc trần" mẹ bé Bắp nói chuyện trước sau bất nhất?

Thêm 1 sao Việt tung tin nhắn, "bóc trần" mẹ bé Bắp nói chuyện trước sau bất nhất? Người mẹ bật điều hòa giữ xác con gái trong căn chung cư suốt 6 năm

Người mẹ bật điều hòa giữ xác con gái trong căn chung cư suốt 6 năm Mẹ Bắp lên tiếng về chiến dịch gây quỹ trên Give.Asia và mối quan hệ với gia đình chồng cũ

Mẹ Bắp lên tiếng về chiến dịch gây quỹ trên Give.Asia và mối quan hệ với gia đình chồng cũ Mẹ bé Bắp: 'Ba mẹ ở quê đi chợ mua đồ nhưng không ai bán, nhà có gì ăn nấy'

Mẹ bé Bắp: 'Ba mẹ ở quê đi chợ mua đồ nhưng không ai bán, nhà có gì ăn nấy' Nóng: Huy Khánh và Mạc Anh Thư ly hôn sau 12 năm chung sống

Nóng: Huy Khánh và Mạc Anh Thư ly hôn sau 12 năm chung sống Nóng: Báo Hàn "bắt gọn" Lee Jong Suk hẹn hò Moon Ga Young, chuyện tình với IU đã toang?

Nóng: Báo Hàn "bắt gọn" Lee Jong Suk hẹn hò Moon Ga Young, chuyện tình với IU đã toang? Mỹ nhân Việt đổi đời chỉ nhờ 1 cái bĩu môi, cả body lẫn nhan sắc đều thăng hạng đỉnh cao sau 8 năm

Mỹ nhân Việt đổi đời chỉ nhờ 1 cái bĩu môi, cả body lẫn nhan sắc đều thăng hạng đỉnh cao sau 8 năm Kỳ thú hiện tượng "Thất tinh liên châu" - 7 hành tinh hội tụ hiếm gặp, ở Việt Nam quan sát được không?

Kỳ thú hiện tượng "Thất tinh liên châu" - 7 hành tinh hội tụ hiếm gặp, ở Việt Nam quan sát được không?