TSMC sẽ sản xuất quy trình N3e sớm hơn so với kế hoạch

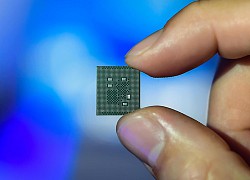

Báo cáo mới từ Morgan Stanley cho thấy TSMC đang đẩy nhanh việc sản xuất chip dựa trên quy trình 3nm nâng cao (N3e) sớm hơn một quý so với kế hoạch ban đầu.

Theo PhoneArena, Morgan Stanley nói năng suất sản xuất của N3e cao hơn dự kiến và xưởng đúc có thể hoàn tất thiết kế của nút N3e vào cuối tháng này. Ban đầu, TSMC dự kiến bắt đầu sản xuất số lượng lớn chip N3e khoảng một năm sau khi N3 được bắt đầu, dự kiến là quý 3/2023.

Tuy nhiên, do năng suất thử nghiệm của N3e đã cao, TSMC muốn bắt đầu sử dụng quy trình này cho mục đích thương mại sớm hơn vào quý 2/2023.

Quy trình sản xuất chip 3nm nâng cao của TSMC sẽ được đẩy nhanh

Nội dung báo cáo cho biết, mật độ logic của quy trình N3e từ TSMC ít hơn khoảng 8% so với N3 ban đầu, giúp tăng năng suất, tăng hiệu suất và giảm năng lượng. Việc chuyển sản xuất N3e sớm trước một quý không ảnh hưởng đến việc sản xuất chip N3 (3nm) ban đầu. TSMC vẫn dự kiến sẽ bắt đầu sản xuất chip N3 từ quý 3 năm nay và giao chúng cho khách hàng vào quý đầu tiên của năm 2023.

Video đang HOT

Các chip được sản xuất bằng quy trình N3 hoặc N3e của TSMC hoặc quy trình 3GAE của Samsung Foundry dự kiến sẽ không xuất hiện trên thị trường cho đến quý 3 hoặc quý 4 năm sau.

Trong khi TSMC vẫn là xưởng đúc hàng đầu trên toàn cầu thì đối thủ cạnh tranh chính của công ty lại đang gặp vấn đề. Samsung được cho là đã bắt đầu bị điều tra gian lận khi một số nhân viên của Samsung Foundry bị giới truyền thông Hàn Quốc buộc tội nói quá về sản lượng chip 4nm của họ. Ví dụ, năng suất cho hoạt động sản xuất chip của Samsung Foundry chỉ đạt 35%, trong khi của TSMC đạt đến 70%. Những con số về sản lượng đáng thất vọng đã khiến Qualcomm phải chuyển đổi và giờ đây hãng sẽ chọn TSMC chịu trách nhiệm sản xuất chip hàng đầu thế hệ tiếp theo của mình, có thể mang tên Snapdragon 8 Gen 2.

Intel, TSMC và Samsung 'bắt tay' phát triển công nghệ xếp chồng chip

Intel, TSMC và Samsung đang cùng nhau thiết lập tiêu chuẩn thống nhất cho các công nghệ đóng gói chip và xếp chồng chip tiên tiến, mở ra nhiều cơ hội phát triển cho ngành sản xuất chip trong tương lai.

Cụ thể, Intel, TSMC và Samsung đã đăng tải thông báo rằng họ sẽ cùng thành lập một liên minh hợp tác về đóng gói và xếp chồng chip thế hệ tiếp theo. Đây là những bước cuối cùng trong sản xuất chất bán dẫn trước khi chip được gắn lên bảng mạch in và lắp ráp vào các thiết bị điện tử.

Bên cạnh ba nhà sản xuất chip lớn nhất thế giới, một số nhà phát triển chip hàng đầu và những gã khổng lồ công nghệ, từ ASE Technology Holding (nhà cung cấp đóng gói và thử nghiệm chip lớn nhất thế giới), Advanced Micro Devices, Qualcomm và Arm, đến Google Cloud, Meta và Microsoft... cũng sẽ tham gia liên minh. Ngoài ra, liên minh cho biết họ vẫn đang mở rộng cửa để chào đón nhiều công ty khác.

Đóng gói chip đang trở thành xu hướng

Trước đây, việc đóng gói chip được coi là ít quan trọng và đòi hỏi công nghệ cao hơn so với việc tự sản xuất chip. Thế nhưng, lĩnh vực này đang nổi lên như một chiến trường lớn đối với các nhà sản xuất chip hàng đầu thế giới, cụ thể ở đây là Samsung, Intel và TSMC, khi họ "vắt chân lên cổ" để chạy theo cuộc đua sản xuất những con chip mạnh hơn bao giờ hết.

Nhìn chung, đến thời điểm hiện tại thì sự phát triển chất bán dẫn chủ yếu tập trung vào việc làm thế nào để "ép" nhiều bóng bán dẫn hơn vào một con chip, vì nhiều bóng bán dẫn hơn sẽ đem đến sức mạnh tính toán lớn hơn. Nhưng khi không gian giữa các bóng bán dẫn bị thu hẹp chỉ còn vài nanomet, cách tiếp cận này đang dần trở thành thử thách rất lớn, khiến một số người dự đoán sự kết thúc của định luật Moore - giả thuyết rằng số lượng bóng bán dẫn trên chip tăng gấp đôi sau mỗi hai năm.

Chính vì vậy, các nhà sản xuất chip đang có xu hướng quan tâm và phát triển công nghệ đóng gói chip (chip-packaging) và xếp chồng chip (chip-stacking), với kỳ vọng có thể đóng gói và xếp chồng các chip nhỏ có các chức năng và tính năng khác nhau lại với nhau một cách hiệu quả nhất.

Không thể "ép" nhiều bóng bán dẫn hơn, các nhà sản xuất chip chuyển sang công nghệ đóng gói chip và xếp chồng chip

Liên minh vừa thành lập nhằm thiết lập một tiêu chuẩn đóng gói chip duy nhất, được gọi là Universal Chiplet Interconnect Express (UCIe), để tạo ra một hệ sinh thái mới và sự hợp tác nhiên liệu trong phân khúc đóng gói và xếp chồng. Cách tốt hơn để kết hợp các loại chip khác nhau - hay còn gọi là chiplet - trong một gói có thể tạo ra một hệ thống chip mạnh mẽ hơn.

Trong các thành viên của liên minh, Google và AMD là hai trong số những công ty đầu tiên áp dụng công nghệ xếp chồng chip 3D tiên tiến nhất của TSMC.

Apple và Huawei không tham gia liên minh

Apple và Huawei không tham gia liên minh do Intel, TSMC và Samsung tạo ra, nhưng không đồng nghĩa rằng họ không quan tâm đến công nghệ đóng góp chip.

Cụ thể, Apple là công ty đầu tiên sử dụng công nghệ đóng gói chip của TSMC, được phát triển nội bộ vào năm 2016, và đã tiếp tục sử dụng các công nghệ này trong bộ vi xử lý iPhone mới nhất (tức A15 Bionic).

Trong khi đó, công ty công nghệ lớn nhất Trung Quốc, Huawei Technologies, đang nỗ lực phát triển công nghệ đóng gói và xếp chồng chip tân tiến riêng. Nhận định bởi Nikkei Asia, động thái của Huawei nhằm giảm bớt tác động của các lệnh trừng phạt mà Mỹ đã áp đặt lên công ty này.

Chuẩn kết nối hoàn chỉnh mở ra tương lai cho ngành sản xuất SoC

Được tạo ra để cung cấp một tiêu chuẩn kết nối hoàn chỉnh cho công nghệ đóng gói và xếp chồng chip, UCIe được mong đợi là sẽ giúp những người dùng cuối (ở đây là các nhà sản xuất các bộ chip đóng gói và xếp chồng) có thể dễ dàng kết hợp các thành phần chiplet. Từ đó, tạo điều kiện thuận lợi trong xây dựng các hệ thống tuỳ chỉnh trên chip (SoC) từ các bộ phận của các nhà cung cấp khác nhau.

TSMC, MediaTek thuê hơn 10.000 nhân viên trong năm nay  Các công ty Đài Loan vẫn phải đối mặt với sự thúc đẩy mạnh mẽ của toàn cầu khi cuộc khủng hoảng chip chưa chấm dứt. Theo Nikkei, hai nhà sản xuất chip hàng đầu của Đài Loan có kế hoạch thuê hơn 10.000 kỹ sư trong năm nay, để thúc đẩy kế hoạch mở rộng mạnh mẽ và duy trì lợi thế...

Các công ty Đài Loan vẫn phải đối mặt với sự thúc đẩy mạnh mẽ của toàn cầu khi cuộc khủng hoảng chip chưa chấm dứt. Theo Nikkei, hai nhà sản xuất chip hàng đầu của Đài Loan có kế hoạch thuê hơn 10.000 kỹ sư trong năm nay, để thúc đẩy kế hoạch mở rộng mạnh mẽ và duy trì lợi thế...

Các thương hiệu lớn Trung Quốc rủ nhau rời xa Android?08:38

Các thương hiệu lớn Trung Quốc rủ nhau rời xa Android?08:38 iPhone có một tính năng không phải ai cũng biết00:36

iPhone có một tính năng không phải ai cũng biết00:36 Câu chuyện thú vị về bài hát khiến Windows 'đứng hình'02:25

Câu chuyện thú vị về bài hát khiến Windows 'đứng hình'02:25 Lý do bất ngờ khiến Windows 7 khởi động chậm chạp06:56

Lý do bất ngờ khiến Windows 7 khởi động chậm chạp06:56 Canh bạc AI của Apple nhằm 'hạ bệ' Samsung08:44

Canh bạc AI của Apple nhằm 'hạ bệ' Samsung08:44 Vì sao pin smartphone Android kém hơn sau khi cập nhật phần mềm02:20

Vì sao pin smartphone Android kém hơn sau khi cập nhật phần mềm02:20 Windows 11 chiếm bao nhiêu dung lượng ổ cứng?01:07

Windows 11 chiếm bao nhiêu dung lượng ổ cứng?01:07 5 điều nhà sản xuất smartphone không nói cho người mua08:58

5 điều nhà sản xuất smartphone không nói cho người mua08:58 One UI 7 đến với dòng Galaxy S2103:50

One UI 7 đến với dòng Galaxy S2103:50Tiêu điểm

Tin đang nóng

Tin mới nhất

Ra mắt dòng mô hình AI mạnh nhất dành cho người viết phần mềm

Apple phát triển công nghệ hỗ trợ điều khiển thiết bị bằng tín hiệu não

Các nhà thiên văn Australia phát hiện 5 hành tinh mới

Người dùng điện thoại Android sẽ được nâng cấp tính năng chống lừa đảo

Google DeepMind công bố AI khoa học 'đột phá'

Google sẽ tích hợp Gemini vào các ô tô có hệ điều hành android

Apple dùng AI cải thiện thời gian sử dụng pin cho iPhone

Hàng triệu máy tính gặp nguy hiểm vì bo mạch chủ Asus

Robot hình người của Trung Quốc 'bắt chước' vươn vai như con người

Ngân hàng đẩy mạnh ứng dụng công nghệ số:Tăng cạnh tranh, nâng hiệu quả

One UI 7 đến với dòng Galaxy S21

Sắp có ứng dụng 'chuyển nhà' dễ dàng cho Windows 11

Có thể bạn quan tâm

Toàn cảnh đám cưới đẹp như mơ của Hồ Quỳnh Hương ở tuổi 45

Sao việt

23:51:32 16/05/2025

Phản ứng của em gái Trấn Thành khi lần đầu đóng cảnh 'yêu đương nồng nhiệt'

Hậu trường phim

23:48:13 16/05/2025

Rộ video Wren Evans hôn đắm đuối 1 cô gái, còn có "phản ứng lạ" gây tranh cãi?

Nhạc việt

23:41:24 16/05/2025

Mỹ nhân 54 tuổi vẫn cùng con gái đi học đại học, trẻ hơn bạn cùng lớp kém 36 tuổi mới sốc

Phim châu á

23:33:59 16/05/2025

Nam kỹ sư chinh phục nữ kế toán, được MC nhận xét như dành cho nhau

Tv show

23:01:06 16/05/2025

Mỹ nhân 'Playboy' Pamela Anderson giải thích về mái tóc gây tranh cãi

Sao âu mỹ

22:45:57 16/05/2025

Yêu nhau gần 2 năm, đến khi thấy người yêu bước lên xe Porsche, tôi mới hiểu đằng sau nụ cười ngọt ngào là một sự thật phũ phàng

Góc tâm tình

22:36:19 16/05/2025

Danh tính 9 người thương vong trong vụ sạt lở ở Lai Châu

Tin nổi bật

22:34:02 16/05/2025

Công an Hà Nội thu giữ 100 tấn thực phẩm chức năng, thiết bị y tế giả

Pháp luật

22:20:06 16/05/2025

Ukraine sẵn sàng ngừng bắn vô điều kiện

Thế giới

22:15:47 16/05/2025

Mozilla Firefox cập nhật hai bản vá lỗi bảo mật quan trọng

Mozilla Firefox cập nhật hai bản vá lỗi bảo mật quan trọng Những dự báo về công nghệ và tự động hóa trong năm 2022

Những dự báo về công nghệ và tự động hóa trong năm 2022

TSMC kêu gọi Mỹ đưa các công ty nước ngoài vào hỗ trợ ngành chip

TSMC kêu gọi Mỹ đưa các công ty nước ngoài vào hỗ trợ ngành chip TSMC sắp sản xuất chip 3nm cho iPhone và Mac 2023

TSMC sắp sản xuất chip 3nm cho iPhone và Mac 2023 Intel: Ưu tiên của Mỹ không nên là TSMC

Intel: Ưu tiên của Mỹ không nên là TSMC Sản lượng chip của Đài Loan đạt kỷ lục vào năm nay

Sản lượng chip của Đài Loan đạt kỷ lục vào năm nay Yêu cầu dữ liệu chip của Mỹ có thể mở đường cho các nước khác làm theo

Yêu cầu dữ liệu chip của Mỹ có thể mở đường cho các nước khác làm theo TSMC khẳng định không tiết lộ chi tiết thông tin khách hàng cho Mỹ

TSMC khẳng định không tiết lộ chi tiết thông tin khách hàng cho Mỹ iPhone và máy Mac trang bị chip 3nm vào năm sau

iPhone và máy Mac trang bị chip 3nm vào năm sau Sản xuất chip 3nm của TSMC ưu tiên cho Apple

Sản xuất chip 3nm của TSMC ưu tiên cho Apple Samsung sản xuất chip 3nm số lượng lớn vào năm sau

Samsung sản xuất chip 3nm số lượng lớn vào năm sau Apple, Intel sẽ là hai hãng đầu tiên sản xuất chip bằng tiến trình 3nm của TSMC

Apple, Intel sẽ là hai hãng đầu tiên sản xuất chip bằng tiến trình 3nm của TSMC Sự cố mất điện tại Đài Loan có thể gây hại Apple

Sự cố mất điện tại Đài Loan có thể gây hại Apple Các nhà sản xuất chip trấn an trước tình hình quân sự Nga - Ukraine

Các nhà sản xuất chip trấn an trước tình hình quân sự Nga - Ukraine Sắp được dùng internet vệ tinh Starlink tại Việt Nam

Sắp được dùng internet vệ tinh Starlink tại Việt Nam Lần đầu chụp được ảnh cực quang trên sao Hỏa

Lần đầu chụp được ảnh cực quang trên sao Hỏa Apple chuẩn bị tung iPhone 'khác biệt nhất lịch sử'

Apple chuẩn bị tung iPhone 'khác biệt nhất lịch sử' GS.TSKH Hồ Sĩ Thoảng: Khoa học công nghệ có vai trò mở đường, tạo đột phá

GS.TSKH Hồ Sĩ Thoảng: Khoa học công nghệ có vai trò mở đường, tạo đột phá Nỗi ám ảnh thời lượng pin iPhone sẽ biến mất nhờ iOS 19

Nỗi ám ảnh thời lượng pin iPhone sẽ biến mất nhờ iOS 19 Apple sẽ sử dụng AI để quản lý pin trên iPhone

Apple sẽ sử dụng AI để quản lý pin trên iPhone Top 4 camera Tapo ngoài trời bền đẹp, chất lượng cao

Top 4 camera Tapo ngoài trời bền đẹp, chất lượng cao Tin tặc dùng AI để dò mật khẩu người dùng

Tin tặc dùng AI để dò mật khẩu người dùng Vụ vợ bị chồng 'xử' tại chỗ làm ở Hải Dương: hé lộ động cơ gây án sốc

Vụ vợ bị chồng 'xử' tại chỗ làm ở Hải Dương: hé lộ động cơ gây án sốc Vụ tai nạn giao thông ở Vĩnh Long: Thực hư thông tin "bắt khẩn cấp một cán bộ cấp cao"?

Vụ tai nạn giao thông ở Vĩnh Long: Thực hư thông tin "bắt khẩn cấp một cán bộ cấp cao"? Người phụ nữ Indonesia nhiễm trùng sau phẫu thuật thẩm mỹ tại TPHCM

Người phụ nữ Indonesia nhiễm trùng sau phẫu thuật thẩm mỹ tại TPHCM

UAE tặng ông Trump một giọt dầu mỏ

UAE tặng ông Trump một giọt dầu mỏ Đến bệnh viện để phẫu thuật nhưng bác sĩ lại là bạn trai cũ, anh ấy nói câu này khiến trái tim tôi "run rẩy"

Đến bệnh viện để phẫu thuật nhưng bác sĩ lại là bạn trai cũ, anh ấy nói câu này khiến trái tim tôi "run rẩy" Clip sốc: Mỹ nhân Trung Quốc bị đuổi khỏi thảm đỏ Cannes vì hành động đáng xấu hổ với Tom Cruise

Clip sốc: Mỹ nhân Trung Quốc bị đuổi khỏi thảm đỏ Cannes vì hành động đáng xấu hổ với Tom Cruise

Cô gái bị đánh gục trong quán cà phê ở TPHCM yêu cầu bồi thường 900 triệu

Cô gái bị đánh gục trong quán cà phê ở TPHCM yêu cầu bồi thường 900 triệu Hoa hậu Ý Nhi nịnh dì Ly Miss World vẫn out top 20 tức tưởi, bị bạn trai "hại"?

Hoa hậu Ý Nhi nịnh dì Ly Miss World vẫn out top 20 tức tưởi, bị bạn trai "hại"? Khai trừ đảng, buộc thôi việc giáo viên đưa người nhà vào trường đánh giáo viên khác

Khai trừ đảng, buộc thôi việc giáo viên đưa người nhà vào trường đánh giáo viên khác Cô gái 2 lần sinh con cho "thầy ông nội" mất tích bí ẩn, giống hệt Diễm My?

Cô gái 2 lần sinh con cho "thầy ông nội" mất tích bí ẩn, giống hệt Diễm My? Vụ phụ xe tử vong khi cố chặn xe buýt đang trôi: Nghi quên kéo phanh tay

Vụ phụ xe tử vong khi cố chặn xe buýt đang trôi: Nghi quên kéo phanh tay Căng: Điều tra khẩn Trần Kiều Ân và hơn 20 sao hạng A Trung Quốc, "công chúa Cello" bị liệt vào tội đặc biệt

Căng: Điều tra khẩn Trần Kiều Ân và hơn 20 sao hạng A Trung Quốc, "công chúa Cello" bị liệt vào tội đặc biệt Chủ tịch Công ty dược Sơn Lâm hối lộ hơn 71 tỷ đồng để trót lọt đưa thuốc vào bệnh viện

Chủ tịch Công ty dược Sơn Lâm hối lộ hơn 71 tỷ đồng để trót lọt đưa thuốc vào bệnh viện Người phụ nữ chết ngay tại ngân hàng vì ốm nặng cũng phải ra tận nơi rút tiền

Người phụ nữ chết ngay tại ngân hàng vì ốm nặng cũng phải ra tận nơi rút tiền Đông Hùng: Thiếu gia thay mẹ trả nợ, rửa bát thuê, hot lại nhờ bè cho Võ Hạ Trâm

Đông Hùng: Thiếu gia thay mẹ trả nợ, rửa bát thuê, hot lại nhờ bè cho Võ Hạ Trâm