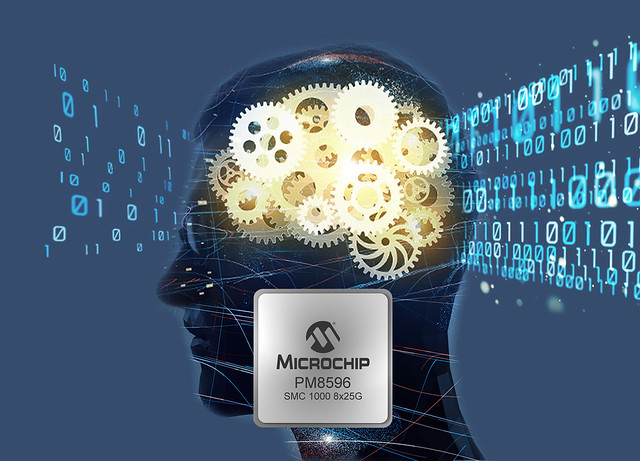

Microchip gia nhập thị trường cơ sở hạ tầng bộ nhớ cho trung tâm dữ liệu

Microchip Technology Inc. vừa công bố dòng sản phẩm trung tâm dữ liệu mở rộng và gia nhập thị trường cơ sở hạ tầng bộ nhớ với bộ điều khiển bộ nhớ nối tiếp đầu tiên trên thị trường.

Khi nhu cầu điện toán của trí tuệ nhân tạo (AI) và máy học (machine learning) phải xử lý khối lượng công việc ngày càng tăng, bộ nhớ DRAM được gắn song song truyền thống đã trở thành rào cản đối với những CPU thế hệ tiếp theo, vốn yêu cầu số lượng kênh bộ nhớ cao hơn để cung cấp thêm băng thông bộ nhớ. Mẫu SMC 1000 8×25G với phương thức gắn nối tiếp cho phép CPU và các SoC trung tâm điện toán khác có thể tận dụng số kênh bộ nhớ nhiều hơn bốn lần so với DRAM DDR4 gắn song song có cùng cấu trúc chân cắm. Bộ điều khiển bộ nhớ nối tiếp của Microchip cung cấp băng thông bộ nhớ cao hơn và không phụ thuộc vào những nền tảng nặng về tính xử lý với độ trễ cực thấp.

Khi số lượng nhân xử lý trong CPU tăng, băng thông bộ nhớ trung bình mà mỗi nhân xử lý có thể sử dụng sẽ giảm bởi các chip CPU và SoC không thể tăng giảm số lượng giao diện DDR song song trên cùng một con chip để đáp ứng nhu cầu của số lượng nhân cao hơn. SMC 1000 8×25G tương tác với CPU thông qua giao diện bộ nhớ mở 8 bit (OMI) – bao gồm các làn và cầu nối 25 Gbps để kết nối tới bộ nhớ thông qua giao diện DDR4 3200 72-bit. Kết quả là giảm một cách đáng kể số lượng chân yêu cầu của CPU hoặc SoC chủ trên mỗi kênh bộ nhớ DDR3, cho phép nhiều kênh bộ nhớ có thể sử dụng hơn, đồng thời tăng băng thông bộ nhớ có thể sử dụng.

Một CPU hoặc SoC có hỗ trợ OMI có khả năng sử dụng nhiều loại bộ nhớ với giá thành, công suất và hiệu xuất khác nhau mà không phải tích hợp bộ điều khiển bộ nhớ riêng cho từng loại. Ngược lại, các giao diện bộ nhớ cho CPU và SoC ngày nay thường phải đi liền với các giao thức giao diện DRR cụ thể, ví dụ như DDR4, với những tốc độ của giao diện cụ thể. SMC 1000 8×25G là sản phẩm hạ tầng bộ nhớ đầu tiên trong danh mục sản phẩm của Microchip, cho phép giao diện OMI độc lập với bộ nhớ.

Video đang HOT

Khối lượng công việc được ứng dụng cho trung tâm dữ liệu, yêu cầu sản phẩm bộ nhớ DDIMM dựa trên nền tảng OMI để cho cùng kết quả băng thông hiệu suất cao và độ trễ thấp giống như các sản phẩm bộ nhớ trên nền tảng DRR song song ngày nay. SMC 1000 8×25G của Microchip được thiết kế độ trễ thấp tân tiến đem lại độ trễ dưới 4 ns so với bộ điều khiển DDR tích hợp truyền thống sử dụng LRDIMM. Nhờ đó, các sản phẩm DDIMM trên nền tảng OMI có hiệu suất của băng thông và độ trễ gần như tương tự so với các sản phẩm LRDIMM.

Ông Pete Hazen, phó chủ tịch đơn vị kinh doanh Giải pháp Trung tâm Dữ liệu của Microchip cho biết: “ Microchip hân hạnh giới thiệu thiết bị bộ điều khiển bộ nhớ nối tiếp đầu tiên ra thị trường. Các công nghệ giao diện bộ nhớ mới như Giao diện bộ nhớ mở (OMI) cho phép phạm vi rộng của các ứng dụng SoC hỗ trợ các yêu cầu bộ nhớ ngày càng tăng của ứng dụng trung tâm dữ liệu hiệu suất cao. Microchip bước chân vào thị trường cơ sở hạ tầng bộ nhớ đánh dấu quyết tâm của chúng tôi trong việc cải thiện hiệu suất và hiệu quả của trung tâm dữ liệu.”

SMART Modular, Micron và Samsung Electronics đang xây dựng nhiều mô-đun bộ nhớ kép vi sai Differential Dual-Inline Memory Modules (DDIMM) 84 chân tiết kiệm, với dung lượng đa dạng từ 16 GB đến 256 GB, phù hợp với hệ số dạng DDIMM tiêu chuẩn JEDEC DDR5. Các DDIMM này sẽ tận dụng SMC 1000 8×25G và cắm một cách hoàn hảo với bất kỳ giao diện 25 Gbps tương thích với OMI.

Để hỗ trợ khách hàng xây dựng hệ thống tiêu chuẩn OMI, SMC 1000 được tích hợp với các công cụ chẩn đoán ChipLink, với thiết kế tương thích giúp cung cấp công cụ gỡ lỗi, chẩn đoán, cấu hình và phân tích toàn diện với GUI trực quan.

Theo VN Review

Microchip công bố dòng sản phẩm trung tâm dữ liệu mở rộng

SMC 1000 8x25G cung cấp băng thông bộ nhớ cao theo yêu cầu của những CPU và SoC thế hệ kế tiếp dành cho trí tuệ nhân tạo (AI) và máy học (machine learning)

Khi nhu cầu điện toán của trí tuệ nhân tạo (AI) và máy học (machine learning)phải xử lý khối lượng công việc ngày càng tăng, bộ nhớ DRAM được gắn song song truyền thống đã trở thành rào cản đối với những CPU thế hệ tiếp theo, vốn yêu cầu số lượng kênh bộ nhớ cao hơn để cung cấp thêm băng thông bộ nhớ. Ngày 8/8, Microchip Technology Inc. (Nasdaq: MCHP) đã công bố dòng sản phẩm trung tâm dữ liệu mở rộng và gia nhập thị trường cơ sở hạ tầng bộ nhớ với bộ điều khiển bộ nhớ nối tiếp đầu tiên trên thị trường. Mẫu SMC 1000 8x25G cho phép CPU và các SoC trung tâm điện toán khác có thể tận dụng số kênh bộ nhớ nhiều hơn bốn lần so với DRAM DDR4 gắn song song có cùng cấu trúc chân cắm. Bộ điều khiển bộ nhớ nối tiếp của Microchip cung cấp băng thông bộ nhớ cao hơn và không phụ thuộc vào những nền tảng nặng về tính xử lý với độ trễ cực thấp.

Khi số lượng nhân xử lý trong CPU tăng, băng thông bộ nhớ trung bình mà mỗi nhân xử lý có thể sử dụng sẽ giảm bởi các chíp CPU và SoC không thể tăng giảm số lượng giao diện DDR song song trên cùng một con chip để đáp ứng nhu cầu của số lượng nhân cao hơn. SMC 1000 8x25G tương tác với CPU thông qua giao diện bộ nhớ mở 8 bit (OMI) - bao gồm các làn và cầu nối 25 Gbps để kết nối tới bộ nhớ thông qua giao diện DDR4 3200 72-bit . Kết quả là giảm một cách đáng kể số lượng chân yêu cầu của CPU hoặc SoC chủ trên mỗi kênh bộ nhớ DDR3, cho phép nhiều kênh bộ nhớ có thể sử dụng hơn đồng thời tăng băng thông bộ nhớ có thể sử dụng.

Một CPU hoặc SoC có hỗ trợ OMI có khả năng sử dụng nhiều loại bộ nhớ với giá thành, công suất và hiệu xuất khác nhau mà không phải tích hợp bộ điều khiển bộ nhớ riêng cho từng loại. Ngược lại, các giao diện bộ nhớ cho CPU và SoC ngày nay thường phải đi liền với các giao thức giao diện DRR cụ thể, ví dụ như DDR4, với những tốc độ của giao diện cụ thể. SMC 1000 8x25G là sản phẩm hạ tầng bộ nhớ đầu tiên trong danh mục sản phẩm của Microchip, cho phép giao diện OMI độc lập với bộ nhớ.

Khối lượng công việc được ứng dụng cho trung tâm dữ liệu, yêu cầu sản phẩm bộ nhớ DDIMM dựa trên nền tảng OMI để cho cùng kết quả băng thông hiệu suất cao và độ trễ thấp giống như các sản phẩm bộ nhớ trên nền tảng DRR song song ngày nay. SMC 1000 8x25G của Microchip được thiết kế độ trễ thấp tân tiến đem lại độ trễ dưới bốn ns so với bộ điều khiển DDR tích hợp truyền thống sử dụng LRDIMM. Nhờ đó, các sản phẩm DDIMM trên nền tảng OMI có hiệu xuất của băng thông và độ trễ gần như tương tự so với các sản phẩm LRDIMM.

Ông Pete Hazen, Phó chủ tịch đơn vị kinh doanh Giải pháp Trung tâm Dữ liệu của Microchip cho biết: "Microchip hân hạnh giới thiệu thiết bị bộ điều khiển bộ nhớ nối tiếp đầu tiên ra thị trường. Các công nghệ giao diện bộ nhớ mới như Giao diện bộ nhớ mở (OMI) cho phép phạm vi rộng của các ứng dụng SoC hỗ trợ các yêu cầu bộ nhớ ngày càng tăng của ứng dụng trung tâm dữ liệu hiệu suất cao. Microchip bước chân vào thị trường cơ sở hạ tầng bộ nhớ đánh dấu quyết tâm của chúng tôi trong việc cải thiện hiệu xuất và hiệu quả của trung tâm dữ liệu."

Ông Steve Fields, Kiến trúc sư trưởng của IBM Power Systems, cho biết: "Yêu cầu về khối lượng công việc của khách hàng của IBM ngày càng yêu cầu nhiều bộ nhớ hơn, đó là lý do vì sao chúng tôi đã đưa ra quyết định có tính chiến lược cho các giao diện bộ nhớ của bộ xử lý POWER sử dụng giao diện tiêu chuẩn OMI để tăng băng thông bộ nhớ. IBM đánh giá cao sự hợp tác với Microchip để cung cấp giải pháp này."

SMART Modular, Micron và Samsung Electronics đang xây dựng nhiều Mô-đun bộ nhớ kép vi sai Differential Dual-Inline Memory Modules (DDIMM) 84 chân tiết kiệm, với dung lượng đa dạng từ 16 GB đến 256 GB, phù hợp với hệ số dạng DDIMM tiêu chuẩn JEDEC DDR5. Các DDIMM này sẽ tận dụng SMC 1000 8x25G và cắm một cách hoàn hảo với bất kỳ giao diện 25 Gbps tương thích với OMI.

Myron Slota, Chủ tịch OpenCAPI Consortium, cho biết: "Tiêu chuẩn Giao diện bộ nhớ mở (OMI) cung cấp giao diện bộ nhớ nối tiếp tiết kiệm chân, vì vậy một phạm vi rộng rãi của các ứng dụng CPU và SoC có thể vừa tăng giảm băng thông bộ nhớ vừa có thể chuyển đổi hoàn hảo giữa các loại bộ nhớ mới xuất hiện ngày càng nhiều, như bộ nhớ lớp lưu trữ (storage class memory) mà không gặp vấn đề gì. OpenCAPI cung cấp máy chủ lưu trữ và IP mục tiêu miễn phí duy trì, cũng như việc thúc đẩy một loạt các sáng kiến đa dạng để bảo đảm việc tuân thủ tiêu chuẩn."

Ông Rob Sprinkle, kỹ thuật viên trưởng cấu trúc nền tảng của Google LLC, cho biết: "Khách hàng của Google được hưởng lợi từ các ứng dụng chuyên sâu về dữ liệu như máy học và phân tích dữ liệu đòi hỏi phải có bộ nhớ hiệu xuất cao. Google ủng hộ mạnh mẽ các sáng kiến dựa trên tiêu chuẩn mở như Giao diện bộ nhớ mở (OMI), cung cấp giao diện bộ nhớ hiệu xuất cao để đáp ứng các mục tiêu về hiệu xuất của băng thông và độ trễ quan trọng này."

Theo Pháp Luật VN

TSMC hoàn thiện nhà máy, Apple đã có thể thiết kế vi xử lý 5nm  Theo báo cáo từ Digitimes, TSMC - đối tác cung cấp độc quyền vi xử lý A-Series của Apple đã hoàn thiện xong cơ sở hạ tầng sản xuất vi xử lý trên tiến trình 5nm. Như vậy, táo khuyết đã có thể bắt tay vào thiết kế thực tế vi xử lý thế hệ mới nhất của mình. TSMC cho biết thêm,...

Theo báo cáo từ Digitimes, TSMC - đối tác cung cấp độc quyền vi xử lý A-Series của Apple đã hoàn thiện xong cơ sở hạ tầng sản xuất vi xử lý trên tiến trình 5nm. Như vậy, táo khuyết đã có thể bắt tay vào thiết kế thực tế vi xử lý thế hệ mới nhất của mình. TSMC cho biết thêm,...

Apple muốn tạo bước ngoặt cho bàn phím MacBook05:51

Apple muốn tạo bước ngoặt cho bàn phím MacBook05:51 Gemini sắp có mặt trên các thiết bị sử dụng hằng ngày08:26

Gemini sắp có mặt trên các thiết bị sử dụng hằng ngày08:26 Tính năng tìm kiếm tệ nhất của Google sắp có trên YouTube09:14

Tính năng tìm kiếm tệ nhất của Google sắp có trên YouTube09:14 Chiếc iPhone mới thú vị nhất vẫn sẽ được sản xuất tại Trung Quốc00:36

Chiếc iPhone mới thú vị nhất vẫn sẽ được sản xuất tại Trung Quốc00:36 Điện thoại Samsung Galaxy S25 Edge lộ cấu hình và giá bán "chát"03:47

Điện thoại Samsung Galaxy S25 Edge lộ cấu hình và giá bán "chát"03:47 Pin nấm - bước đột phá của ngành năng lượng bền vững08:03

Pin nấm - bước đột phá của ngành năng lượng bền vững08:03 Câu chuyện thú vị về bài hát khiến Windows 'đứng hình'02:25

Câu chuyện thú vị về bài hát khiến Windows 'đứng hình'02:25 Lý do bất ngờ khiến Windows 7 khởi động chậm chạp06:56

Lý do bất ngờ khiến Windows 7 khởi động chậm chạp06:56 Canh bạc AI của Apple nhằm 'hạ bệ' Samsung08:44

Canh bạc AI của Apple nhằm 'hạ bệ' Samsung08:44 Các thương hiệu lớn Trung Quốc rủ nhau rời xa Android?08:38

Các thương hiệu lớn Trung Quốc rủ nhau rời xa Android?08:38 Vì sao pin smartphone Android kém hơn sau khi cập nhật phần mềm02:20

Vì sao pin smartphone Android kém hơn sau khi cập nhật phần mềm02:20Tiêu điểm

Tin đang nóng

Tin mới nhất

Google phát triển trợ lý AI Gemini phiên bản cho trẻ em

Liệu Apple Watch có ảnh hưởng đến thời lượng pin của iPhone

Vì sao sạc nhanh được quan tâm hơn dung lượng pin?

One UI 7 đang khiến nhiều thiết bị Galaxy hao pin nghiêm trọng

Samsung sẽ đưa chip Exynos lên dòng Galaxy S26?

Sanmina tối ưu hóa hoạt động sản xuất tại Malaysia bằng công nghệ Zebra

Google vô tình tiết lộ tương lai của thiết kế Android

Kế hoạch táo bạo đưa trung tâm dữ liệu lên không gian của cựu CEO Google

Thảm họa Galaxy Note 7 của Samsung trong lịch sử smartphone

iPhone 16 có thể dùng được trong bao lâu?

Công nghệ màn hình có thể thay đổi cuộc chơi cho smartphone

4 chiêu thức lừa đảo qua mã QR người dân cần cảnh giác

Có thể bạn quan tâm

Nhà của Jennifer Aniston bị kẻ lạ đột nhập

Sao âu mỹ

22:49:53 07/05/2025

Karen Nguyễn mong thoát mác 'tiểu tam'

Hậu trường phim

22:46:30 07/05/2025

Jennie (BlackPink) chia sẻ về cuộc sống của một CEO

Sao châu á

22:44:22 07/05/2025

Cảnh báo: Nhiễm giun rồng nguy hiểm do ăn món "đặc sản" gỏi cá

Sức khỏe

22:38:38 07/05/2025

Nhan sắc không tuổi của Song Hye Kyo gây sốt

Phong cách sao

22:36:14 07/05/2025

3 Hồng y gốc Á là ứng viên tiềm năng kế nhiệm Giáo hoàng Francis

Thế giới

22:31:16 07/05/2025

Hoa hậu Phương Lê U50 vẫn yêu cuồng nhiệt: Giao 2 công ty cho chồng mới, vừa mang thai tự nhiên

Sao việt

22:26:50 07/05/2025

Nữ nhân viên tuyệt vọng cầu cứu khi bị đồng nghiệp nhốt trong kho đông lạnh

Netizen

22:23:58 07/05/2025

Phú bà hot nhất Chị Đẹp cảnh báo thông tin sai lệch đang bị lan truyền

Nhạc việt

22:22:35 07/05/2025

Người đàn ông bị sét đánh tử vong ngay trước nhà

Tin nổi bật

22:18:49 07/05/2025

Đại học FPT cấp 7 tỷ đồng học bổng thạc sĩ đào tạo “lãnh đạo chuyển đổi số”

Đại học FPT cấp 7 tỷ đồng học bổng thạc sĩ đào tạo “lãnh đạo chuyển đổi số” Thực thi bảo hộ quyền tác giả trên Internet: Khi thách thức ngày càng nghiêm trọng

Thực thi bảo hộ quyền tác giả trên Internet: Khi thách thức ngày càng nghiêm trọng

Giá đắt không phải lý do duy nhất khiến iPhone suy sụp tại Trung Quốc

Giá đắt không phải lý do duy nhất khiến iPhone suy sụp tại Trung Quốc "Bỏ quên" thị trường Việt, Mobiistar đã làm được gì tại Ấn Độ?

"Bỏ quên" thị trường Việt, Mobiistar đã làm được gì tại Ấn Độ? IC Insights: Intel sẽ chiếm lại ngôi vương trong thị trường bán dẫn 2019

IC Insights: Intel sẽ chiếm lại ngôi vương trong thị trường bán dẫn 2019 Apple đang nỗ lực hết mình để tăng trưởng ở thị trường Ấn Độ

Apple đang nỗ lực hết mình để tăng trưởng ở thị trường Ấn Độ Sau khi giảm giá tại Trung Quốc, doanh số iPhone tăng hơn 70%

Sau khi giảm giá tại Trung Quốc, doanh số iPhone tăng hơn 70% Bùng phát kiểu tấn công không cần Internet

Bùng phát kiểu tấn công không cần Internet

Ưu và nhược điểm cần biết về thành phố thông minh

Ưu và nhược điểm cần biết về thành phố thông minh Apple sắp thay đổi lớn về cách ra mắt và phát hành iPhone

Apple sắp thay đổi lớn về cách ra mắt và phát hành iPhone Huyền thoại Skype chính thức đóng cửa vĩnh viễn

Huyền thoại Skype chính thức đóng cửa vĩnh viễn Pro Max sẽ không còn là mẫu iPhone tốt nhất?

Pro Max sẽ không còn là mẫu iPhone tốt nhất? Windows có lỗ hổng nghiêm trọng, Microsoft biết nhưng từ chối sửa

Windows có lỗ hổng nghiêm trọng, Microsoft biết nhưng từ chối sửa Gã khổng lồ AI của UAE tiến vào thị trường Mỹ giữa cuộc đua công nghệ toàn cầu

Gã khổng lồ AI của UAE tiến vào thị trường Mỹ giữa cuộc đua công nghệ toàn cầu Vương Hỷ: Ảnh đế xuất thân cảnh sát, kết buồn với tình đồng giới, giờ bệnh nặng

Vương Hỷ: Ảnh đế xuất thân cảnh sát, kết buồn với tình đồng giới, giờ bệnh nặng Nga công bố danh sách khách mời dự lễ duyệt binh Ngày Chiến thắng

Nga công bố danh sách khách mời dự lễ duyệt binh Ngày Chiến thắng Đoạn ghi âm gây sốc gọi tên 3 người làm Kim Sae Ron đau khổ nhất trước lúc tự tử: Kim Soo Hyun và...

Đoạn ghi âm gây sốc gọi tên 3 người làm Kim Sae Ron đau khổ nhất trước lúc tự tử: Kim Soo Hyun và... Netizen hoang mang trước tin đồn người tố cáo Kim Soo Hyun bị đâm trọng thương, gia đình Kim Sae Ron hoảng loạn cầu cứu!

Netizen hoang mang trước tin đồn người tố cáo Kim Soo Hyun bị đâm trọng thương, gia đình Kim Sae Ron hoảng loạn cầu cứu! Màn chiếm đoạt 1 triệu USD của cựu cán bộ công an Bình Dương

Màn chiếm đoạt 1 triệu USD của cựu cán bộ công an Bình Dương Căng: Phía Kim Soo Hyun đáp trả đoạn ghi âm sốc từ phía Kim Sae Ron, Gold Medalist lập tức gửi đơn kiện

Căng: Phía Kim Soo Hyun đáp trả đoạn ghi âm sốc từ phía Kim Sae Ron, Gold Medalist lập tức gửi đơn kiện

Lãnh Thanh từng là "nam thần" màn ảnh trước khi liệt dây thần kinh số 7

Lãnh Thanh từng là "nam thần" màn ảnh trước khi liệt dây thần kinh số 7 Mẹ nữ sinh Vĩnh Long nghi lén nhận 1 tỷ bồi thường, dân chứng kiến kể điều lạ?

Mẹ nữ sinh Vĩnh Long nghi lén nhận 1 tỷ bồi thường, dân chứng kiến kể điều lạ?

Tài xế vụ nữ sinh Vĩnh Long sắp tỉnh, mẹ ruột đưa ra yêu cầu, Luật sư tung đòn

Tài xế vụ nữ sinh Vĩnh Long sắp tỉnh, mẹ ruột đưa ra yêu cầu, Luật sư tung đòn

Ca sĩ Hồng Hạnh thông báo ly hôn chồng doanh nhân hơn 18 tuổi

Ca sĩ Hồng Hạnh thông báo ly hôn chồng doanh nhân hơn 18 tuổi Thu giữ 200 kg vàng trị giá 330 tỷ VND, hơn 200 tỷ tiền mặt và hàng loạt xe sang của một doanh nhân

Thu giữ 200 kg vàng trị giá 330 tỷ VND, hơn 200 tỷ tiền mặt và hàng loạt xe sang của một doanh nhân Thiếu tướng công an nói về vụ nữ sinh tử vong ở Vĩnh Long

Thiếu tướng công an nói về vụ nữ sinh tử vong ở Vĩnh Long Nóng: Louis Vuitton lên tiếng vụ Lisa (BLACKPINK) mặc trang phục thêu hình mặt người ở vị trí nhạy cảm

Nóng: Louis Vuitton lên tiếng vụ Lisa (BLACKPINK) mặc trang phục thêu hình mặt người ở vị trí nhạy cảm

Cục điều tra VKSND tối cao đến tận nhà làm việc với mẹ nữ sinh ở Vĩnh Long

Cục điều tra VKSND tối cao đến tận nhà làm việc với mẹ nữ sinh ở Vĩnh Long